A Visual Representation for Data and Workflow of HPC Applications

Monday, May 13, 2024 3:00 PM to Wednesday, May 15, 2024 4:00 PM · 2 days 1 hr. (Europe/Berlin)

Foyer D-G - 2nd floor

Research Poster

Performance MeasurementPerformance Tools and Simulators

Information

Poster is on display and will be presented at the poster pitch session.

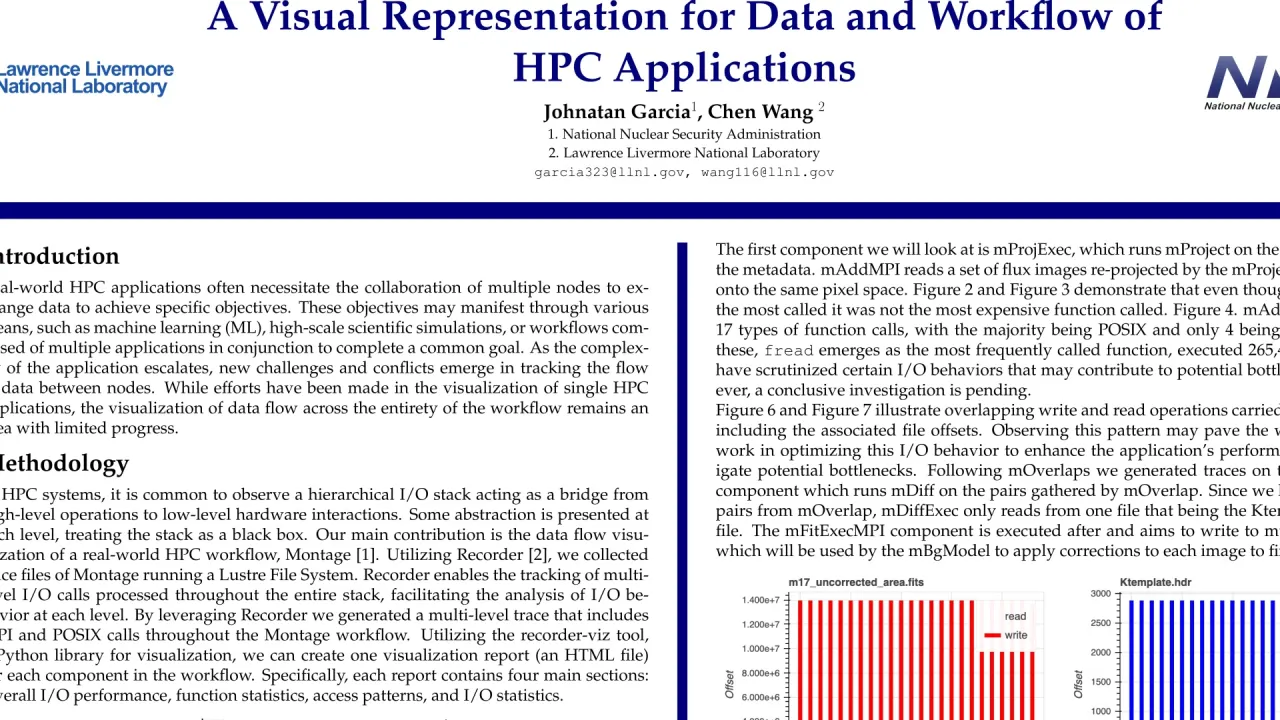

Real-world HPC applications involve multiple nodes exchanging data to achieve specific goals. These goals may manifest through various means, such as machine learning (ML), high-scale scientific simulations, or workflows composed of multiple applications in conjunction to complete a common goal. As the complexity of the workflow increases, new challenges and conflicts emerge in tracking the flow of data between components and nodes. While there have been developments in visualizing I/O behavior of single applications, there has been limited progress in visualizing the data flow across the entire workflow. In this poster, we present an approach to visualize HPC workflows. We leverage Recorder to capture a multi-level trace that includes HDF5, MPI-I/O, and POSIX I/O calls throughout the workflow. We then analyze each component of the workflow and finally create a comprehensive visualization of the entire workflow.

Contributors:

Real-world HPC applications involve multiple nodes exchanging data to achieve specific goals. These goals may manifest through various means, such as machine learning (ML), high-scale scientific simulations, or workflows composed of multiple applications in conjunction to complete a common goal. As the complexity of the workflow increases, new challenges and conflicts emerge in tracking the flow of data between components and nodes. While there have been developments in visualizing I/O behavior of single applications, there has been limited progress in visualizing the data flow across the entire workflow. In this poster, we present an approach to visualize HPC workflows. We leverage Recorder to capture a multi-level trace that includes HDF5, MPI-I/O, and POSIX I/O calls throughout the workflow. We then analyze each component of the workflow and finally create a comprehensive visualization of the entire workflow.

Contributors:

Format

On-site