An FPGA-Based Platform to Evaluate Posit Arithmetic in Next-Generation Processors

Monday, May 22, 2023 3:00 PM to Wednesday, May 24, 2023 5:00 PM · 2 days 2 hr. (Europe/Berlin)

Foyer D-G - 2nd Floor

Research Poster

Emerging HPC Processors and Accelerators

Information

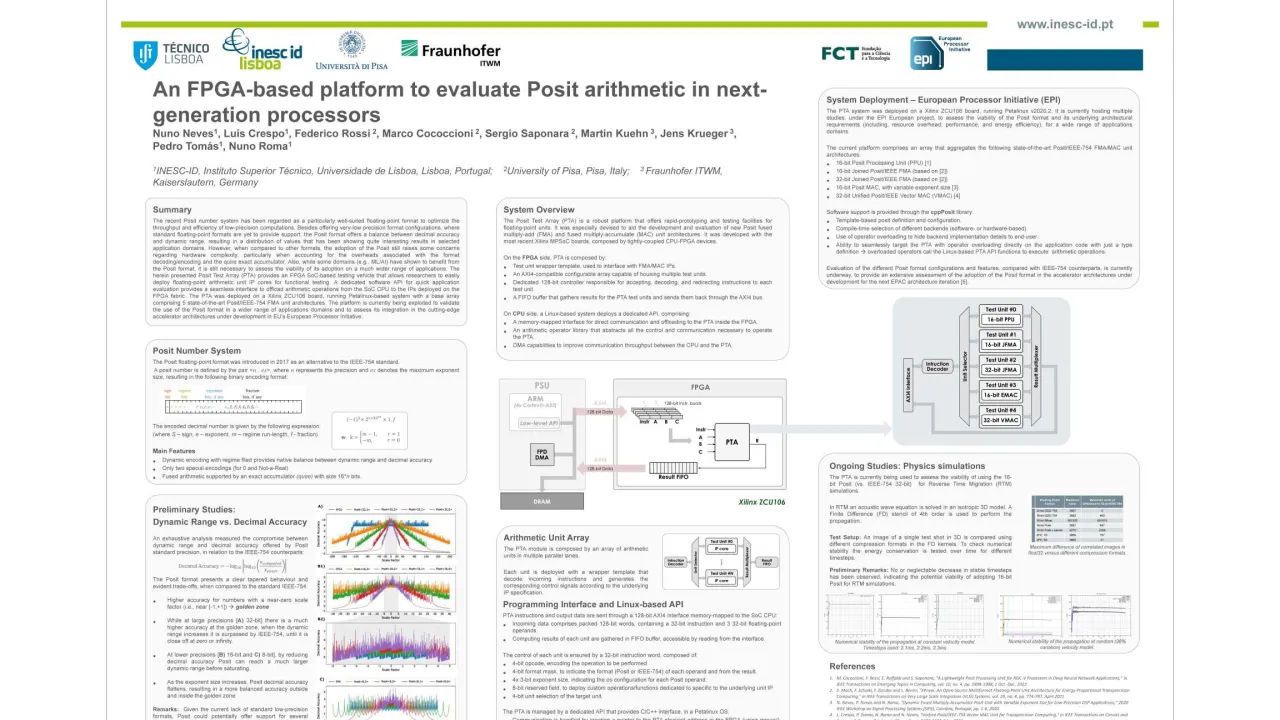

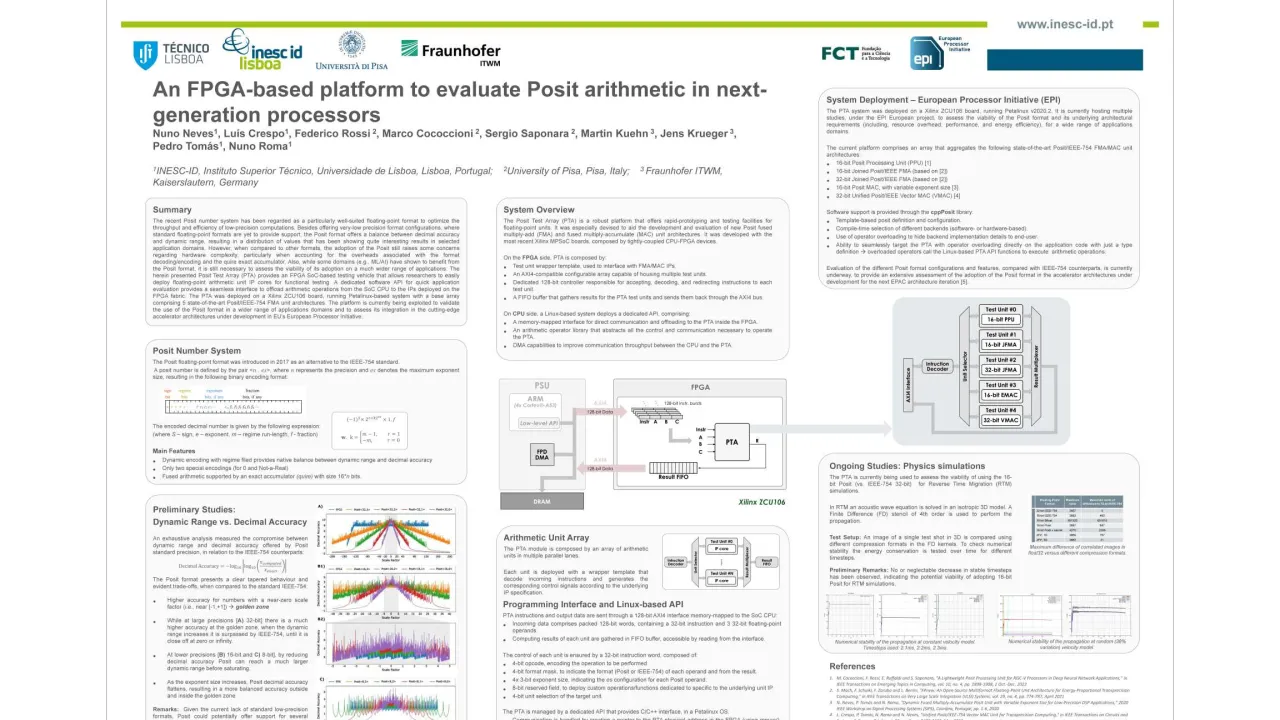

The recent Posit number system has been regarded as a particularly well-suited floating-point format to optimize the throughput and efficiency of low-precision computations. Besides offering very-low precision format configurations, where standard floating-point formats are yet to provide support, the Posit format offers a balance between decimal accuracy and dynamic range, resulting in a distribution of values that has been showing quite interesting results in selected application domains. However, when compared to other formats, the adoption of the Posit still raises some concerns regarding hardware complexity, particularly when accounting for the overheads associated with the format decoding/encoding and the quire exact accumulator. Also, while some domains (e.g., ML/AI) have shown to benefit from the Posit format, it is still necessary to assess the viability of its adoption on a much wider range of applications. The herein presented Posit Test Array (PTA) provides an FPGA SoC-based testing vehicle that allows researchers to easily deploy floating-point arithmetic unit IP cores for functional testing. A dedicated software API for quick application evaluation provides a seamless interface to offload arithmetic operations from the SoC CPU to the IPs deployed on the FPGA fabric. The PTA was deployed on a Xilinx ZCU106 board, running Petalinux-based system with a base array comprising 5 state-of-the-art Posit/IEEE-754 FMA unit architectures. The platform is currently being exploited to validate the use of the Posit format in a wider range of applications domains and to assess its integration in the cutting-edge accelerator architectures under development in EU’s European Processor Initiative.

Contributors:

Contributors:

Format

On-site

Beginner Level

20%

Intermediate Level

50%

Advanced Level

30%