AndesCore™ NX27V RISC-V CPU Processor Core with Vector Extension

IP

Information

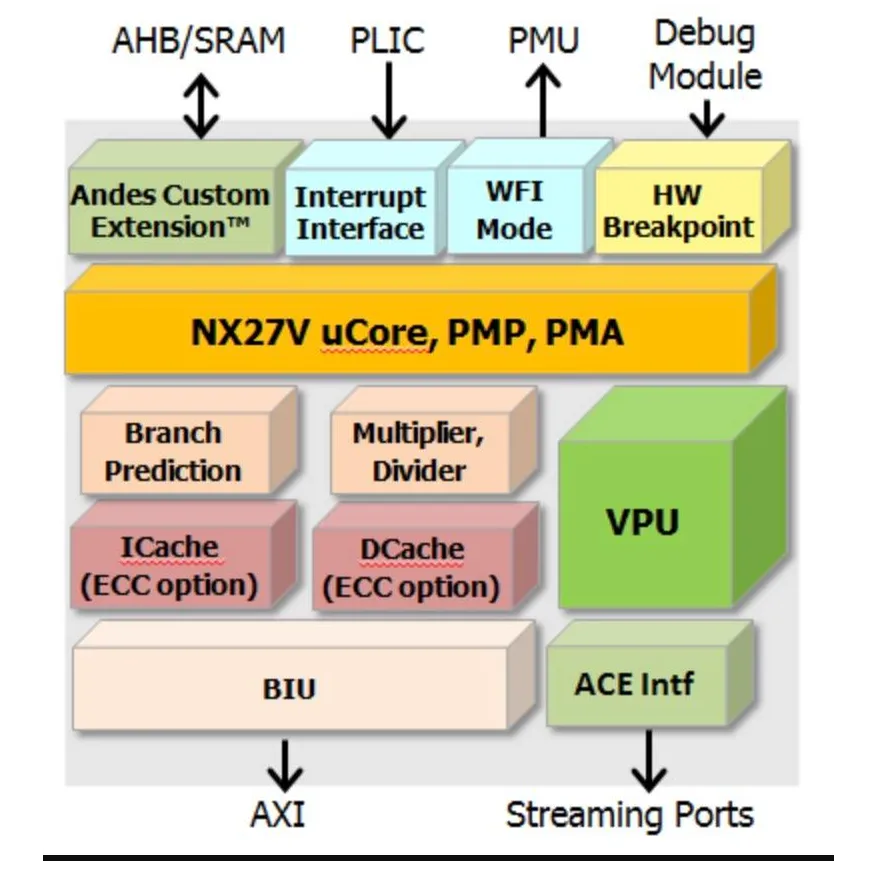

The 64-bit NX27V is a vector processor with 5-stage scalar pipeline supports the latest RISC-V specification, including the IMAFD standard instructions, “C” 16-bit compression instructions, “P” DSP extension instructions, “V” vector extension instructions and “N” for user-level interrupts. It brings enhanced performance in memory subsystem with higher bandwidth and latency reduction by supporting multiple outstanding data access. NX27V features branch prediction, instruction and data caches, local memories, ECC error protection, and Andes Custom Extension™ (ACE) to add proprietary instructions to accelerate performance/power consumption critical spots. It also includes vectored and preemptive interrupts to serve diversified system events. AXI data bus for wide data access, PowerBrake and WFI mode for rich power management, and JTAG debug interface and trace interface for software development support. NX27V contains powerful Vector Processing Unit (VPU). It is ideal for applications with large arrays of data such as machine/deep learning, AR/VR, cryptography, multimedia processing, networking and scientific computing.

• AndeStar™ V5 Instruction Set Architecture, RISC-V technology compliant

• RISC-V vector extension

• Vector Processing Unit (VPU) boosts performance of AI, AR/VR, computer vision, cryptography, and multimedia processing

• Andes extensions for performance and functionality enhancements

• Licensable Andes Custom Extension™ for customized acceleration

• 64-bit CPU architecture, enabling software to address memory beyond 4G bytes

• 16/32-bit mixable instruction format for compacting code density

• Branch predication to speed up control code

• Return Address Stack to speed up procedure returns

• Physical Memory Protection and Programmable Physical Memory Attributes

• MemBoost for heavy memory transactions

• Configurable Platform-Level Interrupt Controller (PLIC) for range of system event scenarios

• vectored interrupt handling

• Advanced CoDense technology